This article is more than 1 year old

HP boffin: Honey! I shrank the PC. To nanometre size, dammit

Right, who here has a really fine set of tweezers

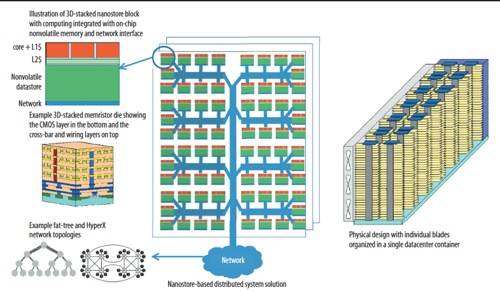

HP boffins have packed layers of RAM, caches and storage into a combined block of memristors and processor cores to create highly scalable "nanostore" systems. It's hoped these little monsters will chew through mountains of data with terrific energy efficiency.

A memristor increases or decreases its electrical resistance depending on the direction of electrons flowing through it. Thus it is possible to store a binary bit in each memristor cell: if a low resistance indicates a '1', a high resistance indicates a '0'. Memristors are non-volatile, like flash, and can be accessed at near-DRAM speed.

The nanostore design appears to place energy efficiency above data retrieval rates. HP Labs fellow Parthasarathy Ranganathan presented the blueprints at the San Jose Server Design Summit this week, according to EE Times.

Ranganathan has a three to five year timescale in mind to develop the technology into a product. The chips will be ideal for crunching through huge datasets that have to be largely or fully in memory to be worked on in parallel. Plus, the nanometre-scale systems should be able to pack more storage capacity into data centres.

He produced an IEEE paper in January 2011 titled From Microprocessors to Nanostores; Rethinking Data-Centric Systems [PDF] in which he discusses the nanostore concept in far more detail.

He wrote:

The key property of nanostores is the colocation of processors with nonvolatile storage, eliminating many intervening levels of the storage hierarchy. All data is stored in a single-level nonvolatile memory datastore that replaces traditional disk and DRAM layers - disk use is relegated to archival backups.

The plan is to collapse a node's compute-and-storage electronics into a single chunk of silicon, allowing data to move between the two halves extremely quickly:

A single nanostore chip consists of multiple 3D-stacked layers of dense silicon nonvolatile memories, such as phase change memories or memristors, with a top layer of power-efficient compute cores. Through-silicon vias are used to provide wide low-energy datapaths between the processors and the datastores.Each nanostore can act as a full-fledged system with a network interface. Individual such nanostores are networked through onboard connectors to form a large-scale distributed system or cluster akin to current large-scale clusters for data-centric computing. The system can support different network topologies, including traditional fat trees or recent proposals like HyperX.

Storage array makers are mulling shoving application software execution into their arrays in one way or another to hasten the transfer of data between processors and information stores; if nanostores escape science-fiction and enter reality, then the technology will be right up the hardware vendors' street.

Doron Kempel's OmniCube is similar to the nanostore, bringing compute, storage and networking together, but does not feature such deep integration at the semiconductor level.

Nanostore and such boffinry can provide a way forward for HP, distancing it further from the tedious Itanium quagmire and the Autonomy absurdity, and give it a dash of cool that could distinguish it from Dell, Cisco and IBM. At heart HP is a technology company and this could be a way back to its core heritage. ®